-

产品及解决方案

-

服务

-

产品及解决方案

-

服务

-

云原生产品及应用平台

-

云服务

【导读】于周详数据收罗体系中,工程师经常会碰到模数转换器(ADC)输出呈现微小误差或者随机颠簸的环境。这种问题往往源在体系内部的电源噪声,特别是压控振荡器(VCO)供电轨上的噪声。这种噪声会激发时钟旌旗灯号抖动,进而被用作ADC的采样时钟,终极致使转换偏差及异样数据的孕育发生。

传统上,因为开关模式电源(SMPS)于开关操作中不成防止地孕育发生噪声,一般不直接用在时钟等敏感供电轨。为了最年夜限度降低偏差,凡是采器具备高噪声按捺能力的低压差线性稳压器(LDO)为要害器件供电。

然而,电源技能最近几年来取患上主要冲破。以 ADI 公司的 LTM8080 为例,该器件将降压型稳压器、后调治双路LDO及噪声按捺技能集成在单一封装。其输出噪声程度可与高机能自力LDO(如 LT3045)相媲美,标记着SMPS也能直接用在低噪声供电场景。

为什么供电轨噪声云云要害?

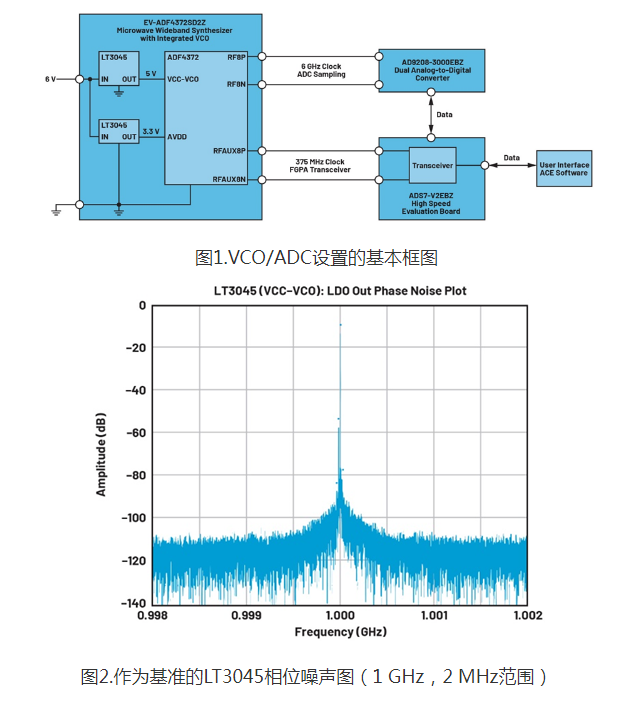

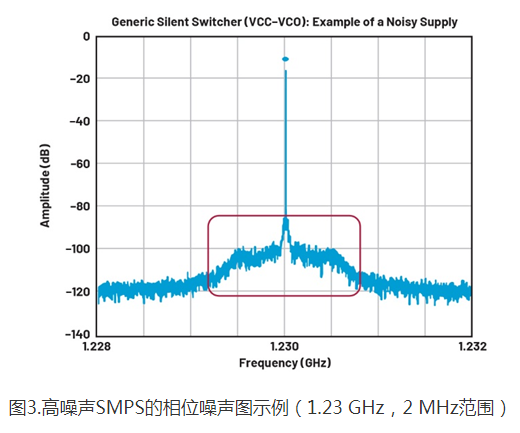

供电轨噪声对于体系机能的影响不容轻忽。例如于图1所示的典型设置中,LT3045 LDO 为 ADF4372 频率合成器的VCO供电,后者为 AD9208 ADC 及 FPGA 板提供时钟。图2所展示的相位噪声图,可作为评估其他电源方案的基准。

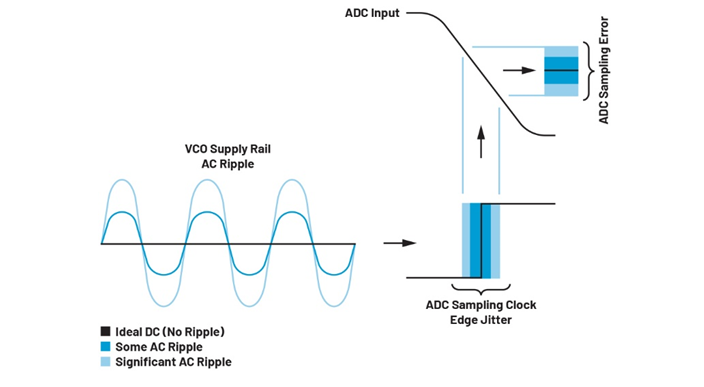

当采用噪声较高的供电轨时,相位噪声边带会较着举高(图3),进而致使ADC采样时钟边缘呈现抖动(图4)。时钟抖动使患上ADC于非抱负时间点对于模仿旌旗灯号举行采样,天生存于位过错的数据字。

位过错可能激发体系层面的问题。例如于安全要害运用中,若数据字唆使的电压高在现实值,可能致使装备提早激活,甚至于未预备好的状况下禁用安全机制,造成严峻后果。

集成架构的上风:SMPS + LDO 一体化方案

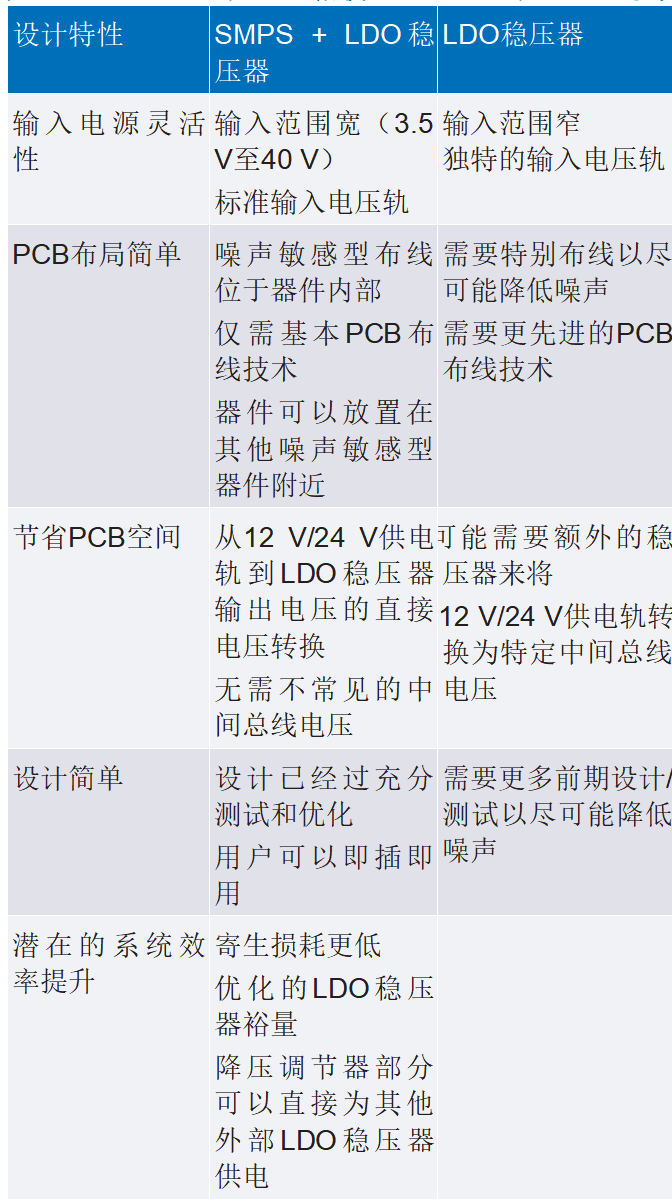

将SMPS与LDO稳压器集成在单一封装,带来多方面的体系上风:

输入矫捷性:可直接接入12 V或者24 V等工业尺度电源轨;

电压裕量节制:撑持VIOC(电压输入‑输出节制)功效,经由过程调治上游SMPS输出,确保LDO始终事情于最好裕量电压,统筹效率与电源按捺比(PSRR);

噪声敏感走线内置:要害旌旗灯号路径于芯片内部完成,降低PCB结构难度;

EMI噪声定向屏蔽:开关噪声被指导阔别LDO输出,防止影响其噪声机能;

扩大能力:除了片内LDO外,还有可撑持外部LDO接入中间总线,晋升设计矫捷性。

此类集成器件于出厂前均颠末周全测试,确保现实机能切合数据手册规格。

实测体现:LTM8080 与 LT3045 对于比

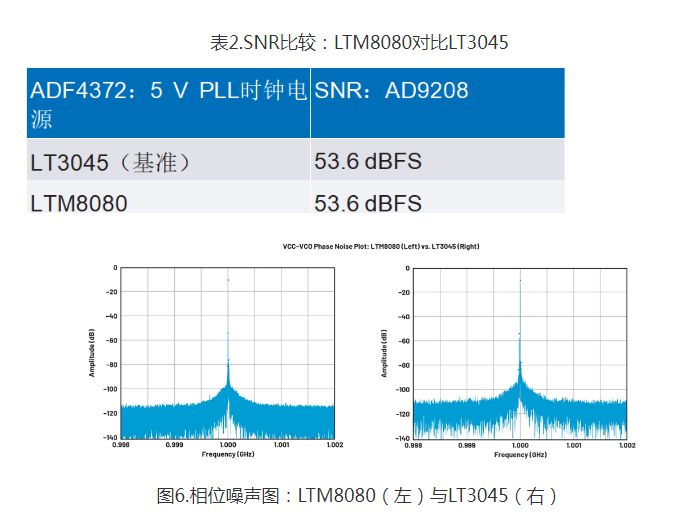

于现实测试中,LTM8080 揭示出与 LT3045 险些一致的噪声按捺能力。如表2所示,二者的信噪比(SNR)很是靠近;图6的相位噪声图进一步验证了LTM8080于噪声节制方面的优异体现。是以,LTM8080 不仅可作为 LT3045 的替换方案,有用降低位过错,还有具有更低的功率损耗及更高的输入电压矫捷性。

结论

测试成果注解,采用进步前辈噪声按捺技能(如EMI噪声屏蔽)的SMPS器件已经可以或许直接为VCO等噪声敏感供电轨供电,于不捐躯信噪比的条件下,兼具高效率与设计矫捷性。只管本文重点会商的是VCO供电场景,但这类高度集成、低噪声的SMPS+LDO架构,一样合用在其他对于电源纯净度有严苛要求的模仿与射频电路,为下一代高机能体系设计提供了靠得住的电源解决方案。

-米兰·(milan)版权所有2016-2025 米兰·(milan)中国数码集团股份有限公司,保留一切权利。