-

产品及解决方案

-

服务

-

产品及解决方案

-

服务

-

云原生产品及应用平台

-

云服务

【导读】于数据转换器的机能评估系统中,线性度偏差是权衡转换精度的焦点指标之一。这个观点可以形象地舆解为:一个抱负的数据转换器该当具有完善的线性相应特征,就像一把刻度匀称的标尺;而现实器件因为制造工艺等因素,其转换特征会偏离抱负直线,这类偏离的最年夜水平就是线性度偏差。工程实践中凡是采用满量程百分比或者LSB(最低有用位)作为计量单元。针对于ADC器件,业界遍及采用码中央连线法举行丈量,此中端点拟合及最好直线拟合是最具代表性的两种评估要领,它们从差别角度展现了转换器的真实机能体现。

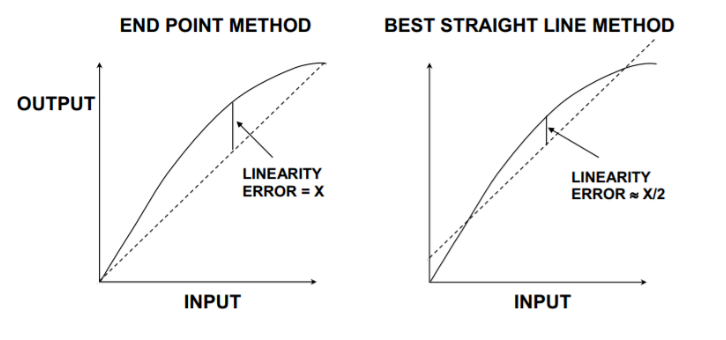

于数据转换器的机能评估系统中,线性度偏差是权衡转换精度的焦点指标之一。这个观点可以形象地舆解为:一个抱负的数据转换器该当具有完善的线性相应特征,就像一把刻度匀称的标尺;而现实器件因为制造工艺等因素,其转换特征会偏离抱负直线,这类偏离的最年夜水平就是线性度偏差。工程实践中凡是采用满量程百分比或者LSB(最低有用位)作为计量单元。针对于ADC器件,业界遍及采用码中央连线法举行丈量,此中端点拟合及最好直线拟合是最具代表性的两种评估要领,它们从差别角度展现了转换器的真实机能体现。如图1所示。

图1:积分线性度偏差的丈量要领(两张图均为统一转换器)

于端点体系中,以经由过程原点及满量程点的直线为基础丈量误差(增益调解后)。对于在数据转换器丈量及节制运用,这是最有效的积分线性度丈量要领(由于偏差预算取决在与抱负通报特征的误差,而非某个随便的“最好拟合”),也是ADI公司凡是利用的要领。

然而,最好直线法确凿可以或许对于交流运用的掉真作出更好的猜测,同时会使数据手册上的“线性度偏差值”降低。最好拟合直线是基在尺度曲线拟合要领,经由过程器件的通报特征画成,最年夜误差即基在该直线测患上。一般来讲,使用这类要领测患上的积分线性度偏差仅为端点法所测值的50%。可见,这类要领很是合适体例美丽的数据手册,但对于偏差预算阐发其实不合用。对于在交流运用,标定掉真比直流线性度更有用,是以,很少需要用最好直线法来界说转换器的线性度。

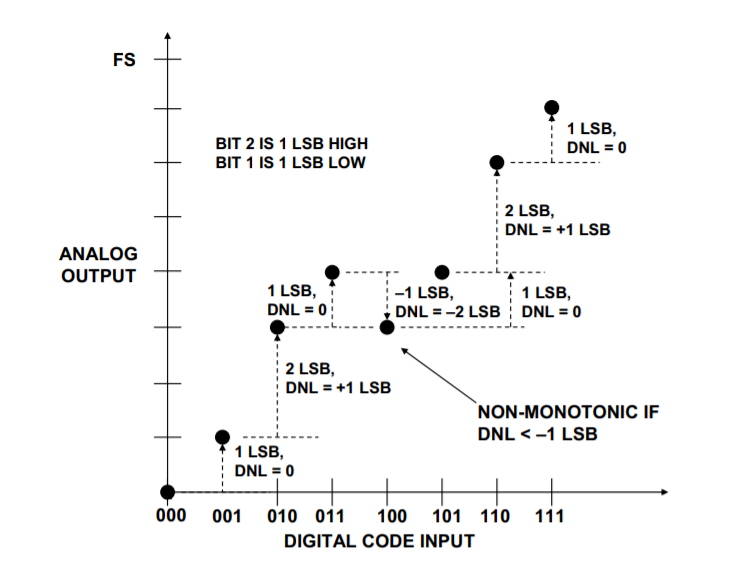

转换器的另外一种非线性度为差分非线性度(DNL)。该项指标与转换器码转换的线性度有关。抱负环境下,数字码每一变化1 LSB,相称在模仿旌旗灯号变化1 LSB。于DAC中,数字码每一变化1 LSB会致使模仿输出正好变化1 LSB;而于ADC中,模仿输入变化1 LSB,数字转换将从一个进入下一个。差分线性度偏差界说为整个通报函数与抱负值1 LSB之间的肆意最年夜误差(或者LSB变化)。

当相称在1 LSB数字变化的模仿旌旗灯号变化量跨越或者不足1 LSB时,即存于DNL偏差。转换器的DNL偏差凡是界说为于转换器整个规模的任何转换点的最年夜DNL。图2所示为DAC及 ADC的非抱负通报函数以和DNL偏差的影响。

图2:非抱负3位DAC及ADC的通报函数

有关DAC DNL的具体阐发见图3。假如DAC的DNL于任何转换点均小在–1 LSB,则该DAC 具备非单调性,即其通报特征含有一个或者多个局部最年夜值或者最小值。DNL年夜在+1 LSB时,不会致使非单调性,但仍旧不睬想。于很多DAC运用中(特别是于非单调性可能使负反馈酿成正反馈的闭环体系中),DAC的单调性很是主要。DAC单调性凡是于数据手册中有明确划定,然而,假如DNL包管低在1 LSB(即|DNL| ≤ 1 LSB),则该器件必然具备单调 性,纵然未明确指出。

图3:DAC差分非线性度详情

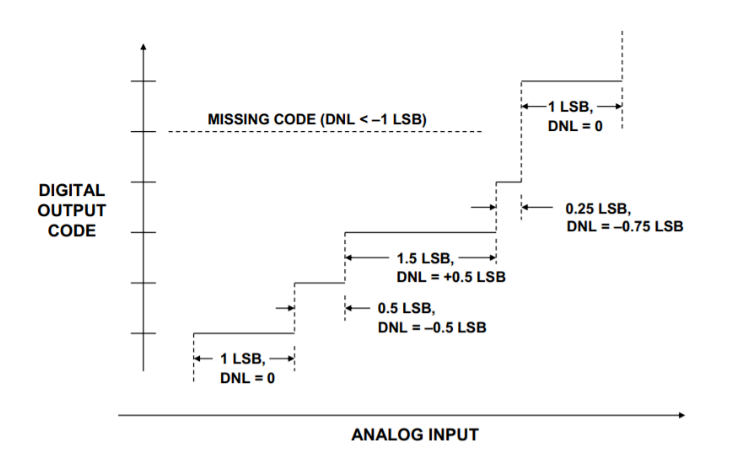

图4越发具体地描写了ADC的DNL。ADC可以为非单调,但ADC中过多的DNL凡是会致使掉码。就像DAC须防止非单调性同样,ADC必需防止掉码。一样,DNL –1 LSB时会致使掉码。

图4:ADC差分非线性度详情

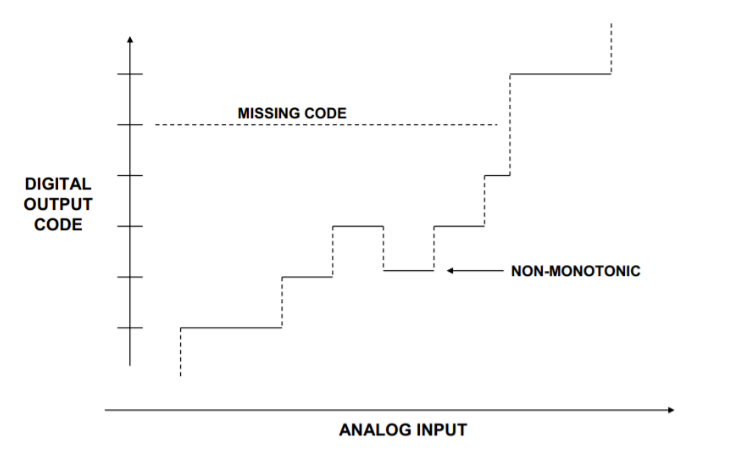

ADC不单可能存于掉码,并且可能具备非单调性,如图5所示。与DAC的环境同样,这会致使严峻问题,特别是于伺服运用中。

图5:ADC掉码和非单调性

DAC中不克不及存于掉码——每一个数字输入字城市孕育发生响应的模仿输出。但DAC可能为非单调性,咱们前面已经提到过这一点。于直接二进制DAC中,最可能孕育发生非单调性前提之处是两个码之间的半量程点:011...11及100...00。假如这里具备孕育发生非单调性前提,通常为由于DAC未获得准确校准或者调解。内置非单调性DAC的逐次迫近ADC一般会孕育发生掉码但连结单调。然而,ADC有可能酿成非单调——一样取决在详细的转换架构。图5显示同时具有非单调性及掉码两种特征的ADC的通报函数。

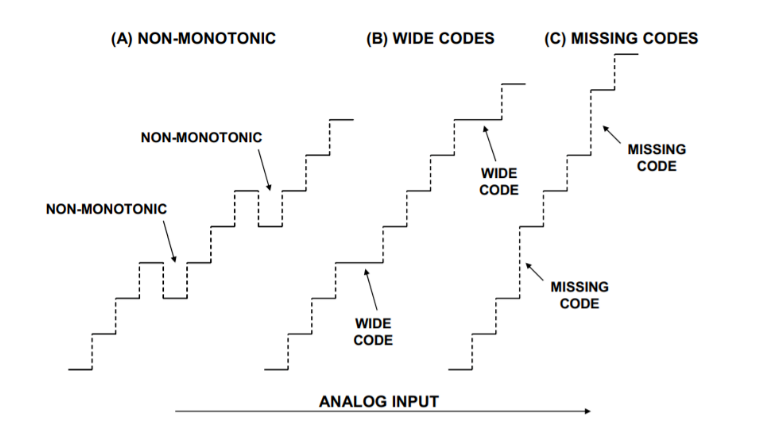

采用分级架构的ADC将输入规模大略分成多段,每一段再分成更小的段——末了获得终极码。该历程详见本书第4章。调解不妥的分级ADC可能于分级点体现出非单调性、宽码或者掉码,别离如图6A、图6B及图6C所示。这种ADC应举行调解,如许因老化或者温度致使的漂移于敏感点孕育发生宽码,而不长短单调性或者掉码。

图6:调解不妥的分级ADC相干偏差

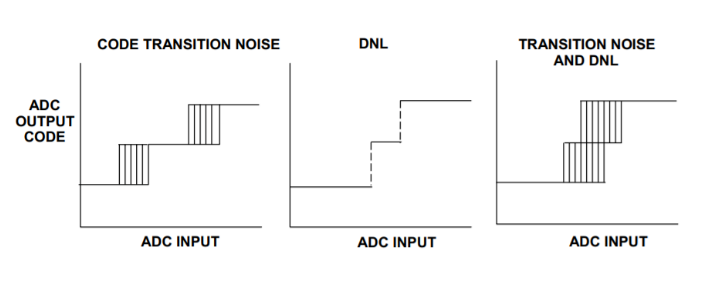

界说掉码比界说非单调性更难。所有ADC自己均存于必然的转换噪声问题,如图7所示(将其想像为DVM末了一名数的相邻值之间的跳动)。跟着分辩率及带宽逐渐变高,致使转换噪声的输入规模可能到达甚至跨越1 LSB。高分辩率宽带ADC一般存于内部噪声源,可能反射到输入,作为有用输入噪声,与旌旗灯号相混淆。这类噪声,特别是与负DNL偏差相联合后,可能使某些(甚至所有)码于整个输入规模内均存于转换噪声。于是,有些码可能没有响应的输入来确保该码为输出,虽然有些输入有时可能会孕育发生该码。

图7:码转换噪声与DNL的组合效应

对于在低分辩率ADC,可以将无掉码界说为转换噪声与DNL的组合,由其包管所有码均必然量(可能为0.2 LSB)的无噪声码。然而,于现代Σ-Δ ADC所实现的极高分辩率下,这是没法实现的,纵然是于低分辩率的宽带宽采样ADC中也没法实现。这些环境下,制造商必需以某些其他方式界说噪声电和蔼分辩率。到底采样哪一种要领其实不主要,但数据手册必需明确指出所用要领和预期机能。

保举浏览:

让液压体系 听话 的邪术道具:深度揭秘节制阀的秘密

征服液压体系的“隐形杀手”:电液体系噪声按捺技能全解析

工程师必读:怎样为卑劣情况选择靠得住的MEMS加快度计

工业范畴的“全能动力”:直流机电技能全景解读与选型指南

简朴易行的动态功率节制要领,让IDAC阔别过热困扰

-米兰·(milan)